Verification Guide For Uvm

Tutorials with links to example codes on eda playground eda playground edit save simulate synthesize systemverilog verilog vhdl and other hdls from your web browser.

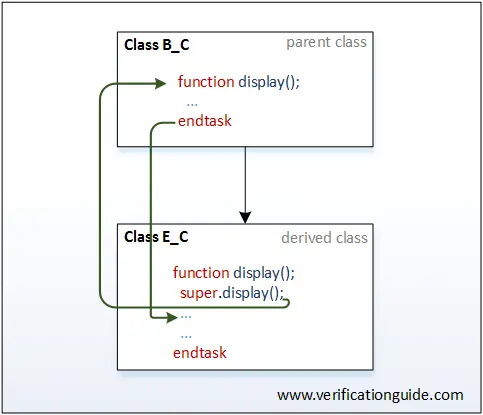

Verification guide for uvm. User defined callback classes can be written by extending the uvm callback class. This guide may have several recommendations to accomplish the same thing and may require some judgment to determine the best course of action. Class cb extends uvm callback. In simple words uvm consists of a set of base classes with methods defined in it the systemverilog verification environment can be developed by extending these base.

Uvm is mainly derived from open verification methodology ovm and is supported by multiple eda vendors like synopsys cadence mentor and aldec. The method can be either a function or task. This guide may have several recommendations to accomplish the same thing and may require some judgment to determine the best course of action. About uvm uvm tutorial uvm interview questions uvm quiz uvm testbench examples.

This guide is a way to apply the uvm 1 1 class reference but is not the only. In it the user defines one or more virtual methods. The uvm 1 2 class reference represents the foundation used to create the uvm 1 2 user s guide. System verilog systemverilog tutorial interview questions systemverilog quiz code library about testbench adder tb example memory model tb example how.

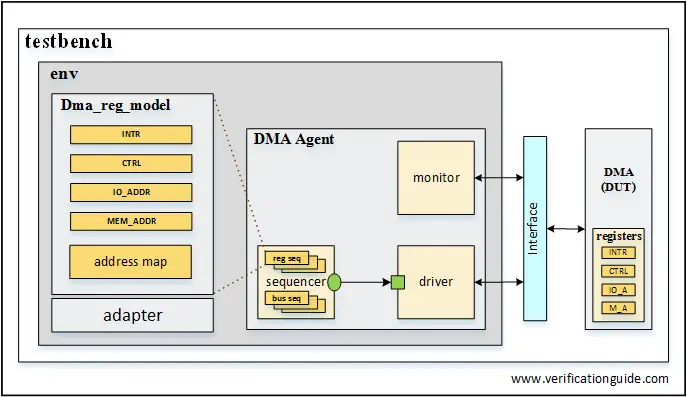

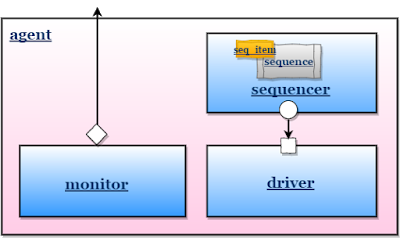

Uvm uvm tutorial uvm callback tutorial uvm interview. These virtual methods are referred to as callback methods these are empty methods with users have the option of overriding them. All these tlm elements are required to send a transaction receive transaction and transport from one component to another. The uvm class library provides generic utilities like configuration databases tlm and component hierarchy in addition to data automation features like copy print and compare.

Uvm tlm the uvm provides tlm library with transaction level interfaces ports exports imp ports and analysis ports. Where each one plays its unique role. Uvm phases are a synchronizing mechanism for the environment. Phases are represented by callback methods a set of predefined phases and corresponding callbacks are provided in uvm component.

The uvm 1 1 class reference represents the foundation used to create the uvm 1 1 user s guide.